Testbench erstellen

Wie man am Bild unten erkennen kann, ist die Datei SimpleLed.vhd zwei mal aufgeführt. Einmal unter Design-Sources und einmal unter Simulation Sources. Das liegt daran, dass diese Datei sowohl in das FPGA synthetisiert als auch simuliert werden soll.

Nun benötigen wir unter den Simulation Sources noch die Testbench-Datei, die dann das Modul SimpleLed als "Unit under Test" (UUT) aufnehmen wird. Dazu erzeugen wir mit dem Add Sources-Kommando eine neue VHDL-Datei:

Daraufhin öffnet sich ein Dialog indem man angibt, dass man Simulations-Dateien hinzufügen (und in diesem Fall erstellen) möchte:

Im nächsten Fenster drückt man auf Create File..., gibt den Dateinamen TestSimpleLed(.vhd) ein und schließt den Vorgang mittels OK und Finish ab.

Für den Namen der Testbench empfehle eine einheitliche Nomenklatur. Ich verwende z.B. immer den Namen des zu testenden Moduls mit dem Prefix „Test“.

In dem nun folgenden Dialog werden die Default-Einstellungen übernommen. Die Eingabe von IO-Ports würde hier auch keinen Sinn machen, da die Testbench über keine IOs verfügen wird.

Der vorgeschlagene Architekturname kann auch so bleiben. Erstens ist er sowieso für nicht weiter relevant, aber im Gegensatz zu "RTL" ist hier "Behavioral" sinnvoll gewählt, da in der Testbench nur das Verhalten der gesamten Schaltung beschrieben wird, aber es nicht notwendig ist, eine synthetisierbare Schaltung zu erzeugen.

Nachdem die Warnung mit "Yes" bestätigt wurde, taucht die neue Datei TestSimpleLed unter Design Sources auf, ist aber mit nichts weiter verbunden. Das folgende Programmgerüst ist dabei erzeugt worden:

TestSimpleLed.vhd

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

-- Uncomment the following library declaration if using

-- arithmetic functions with Signed or Unsigned values

--use IEEE.NUMERIC_STD.ALL;

-- Uncomment the following library declaration if instantiating

-- any Xilinx leaf cells in this code.

--library UNISIM;

--use UNISIM.VComponents.all;

entity TestSimpleLed is

-- Port ( );

end TestSimpleLed;

architecture Behavioral of TestSimpleLed is

begin

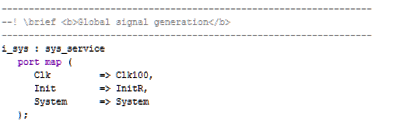

end Behavioral;Die Einbindung der Bibliothek und die entity Definition können so bleiben aber die Architektur muss angepasst werden:

- Das zu testende Modul (UUT) muss eingebunden werden

- Es muss stimuliert werden

- Die Reaktion der uut muss verifiziert werden

Der komplette Code kann von der Seite TestSimpleLed.vhd kopiert werden und wird in den Erläuterungen im Detail beschrieben.

Test durchführen

Wie man erkennen kann sind nun die Dateien TestSimpleLed und SimpleLed miteinander verbunden, da TestSimpleLed das Modul SimpleLed mit dem Namen uut instantiiert hat.

Des weiteren ist die Datei TestSimpleLed mit dem Chipsymbol dargestellt und Fett gedruckt.

Wenn man nun auf "Run Simulation/Run behavioral Simulation" drückt, startet der Simulator und simuliert unsere gerade erstellte Testbench.

Zur Bedienung des Simulators hier in Kürze:

Die Symbole links (1) dienen zum Speichern der Konfiguration und zum Zoomen des Bildausschnitts.

Über Kontextmenü der Signale TestCase und TestErr (2) wird die Farbe der beiden Signale auf Grau eingestellt.

Beim Speichern der Konfiguration wurde der Default-Name verwendet und als relativer Pfad SimpleLed.srcs/sim_1/new/ angegeben. Wenn diese Datei mit dem Projekt verknüpft wird, wird diese Konfiguration bei der nächsten Simulation defaultmäßig wieder geladen.

Am Verlauf ser Signale kann man erkennen, dass während die einzelnen Testcases durchlaufen werden, der Ausgang Led dem Eingang Button folgt.

Am Ende der Simulation geht der TestErr-"Daumen" nach oben und zeigt somit die fehlerfreie Abarbeitung der Testbench an.

Weiter zu den Erläuterungen