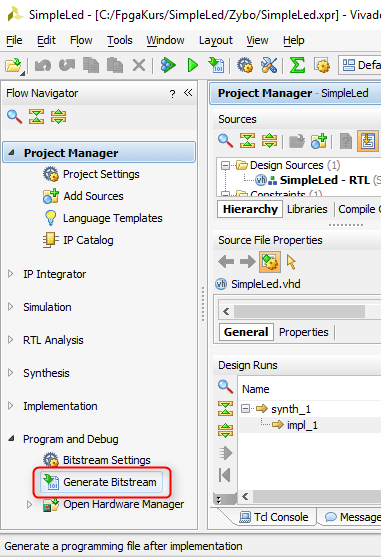

Nachdem das Projekt SimpleLed.xpr über das Generierungs-Skript erzeugt wurde, erscheint links oben im Project Manager im Bereich Sources die Hierarchie dieses Projekts. Man findet hier die beiden Quelldateien SimpleLed.vhd und Zybo.xdc.

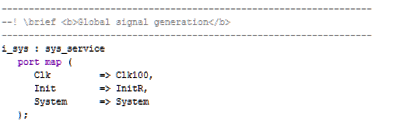

Durch einen Doppelklick auf eine Datei wird sie im Quellcodeeditor von Vivado geöffnet. Die .vhd-Datei dient zur Beschreibung der Funktionalität. Die .xdc-Datei (xdc = xilinx design constraints) dient der Spezifikation des Timings und der IOs.

Die Datei SimpleLed hat auf der linken Seite ein IC-Symbol weil sie als Top-Level deklariert worden ist (über das Kontextmenü). Dadurch wird der Entwicklungsumgebung mitgeteilt, dass die Ein- und Ausgänge von SimpleLed mit den Ein- und Ausgängen des FPGAs übereinstimmen und genauere Angaben dazu (wie Pinout) in der .xdc-Datei stehen.